IMPLEMENTATION OF THE DIVISION OPERATION OF A 32-BIT FLOATING POINT UNIT BASED ON THE IEEE 754 STANDARD IN VERILOG

REGISTRO DOI: 10.69849/revistaft/ni10202501090721

Jordana Alves de Freitas1;

Kátia Lopes Silva2;

Mauro Hemerly Gazzani3

RESUMO

Uma Unidade de Ponto Flutuante (UFP) é um componente essencial de um processador de computador, responsável por realizar operações aritméticas em números de ponto flutuante, seguindo as especificações do padrão IEEE 754. A UPF consiste em uma série de circuitos e lógica projetados para lidar com a representação, manipulação e cálculos de números de ponto flutuante. Ela é responsável por converter os números de ponto flutuante em representações internas adequadas, realizar as operações matemáticas necessárias e fornecer o resultado no formato correto. Este trabalho apresenta a implementação de uma UPF de 32 bits baseada no padrão IEEE 754, utilizando a linguagem Verilog com o objetivo de projetar e simular a unidade durante a implementação da operação aritmética de divisão. A unidade funcional de divisão foi implementada em linguagem Verilog utilizando a plataforma EDA Playground. Onze casos de testes envolvendo situações que podem acontecer no resultado da operação tais como: overflow, underflow e exceções (NaN, infinito) foram simuladas. Os resultados apresentados pela simulação nos onze casos de teste foram aqueles esperados para este tipo de operação com ponto flutuante. As aproximações ocorrem devido ao arredondamento da divisão das mantissas, pois o resultado desta operação deve ser representado em 23 bits. Outra aproximação deve-se ao fato que os operandos chegam à unidade de divisão convertidos em binários e a maioria dos valores em ponto flutuante necessitam de uma quantidade infinita de bits.

Palavras-chave: Unidade de ponto flutuante 32 bits; Verilog; IEEE 754.

ABSTRACT

A Floating-Point Unit (FPU) is an essential component of a computer processor responsible for performing arithmetic operations on floating point numbers, following the specifications of the IEEE 754 standard. The UPF consists of a series of circuits and logic designed to handle the representation, manipulation and calculations of floating-point numbers. It is responsible for converting the floating-point numbers into proper internal representations, performing the necessary mathematical operations and providing the result in the correct format. This work presents the implementation of a 32-bit UPF based on the IEEE 754 standard, using the Verilog language with the objective of designing and simulating the unit during the implementation of the arithmetic operation of division. The division functional unit was implemented in Verilog language using the EDA Playground platform. Eleven test cases involving situations that can happen in the result of the operation such as: overflow, underflow and exceptions (NaN, infinity) were simulated. The results presented by the simulation in the eleven test cases were those expected for this type of operation with floating point. Approximations occur due to rounding when dividing the mantissas, as the result of this operation must be represented in 23 bits. Another approximation is since the operands arrive at the division unit converted into binary and most floating-point values require an infinite number of bits.

Keywords: 32-bit floating point unit; Verilog; IEEE 754.

INTRODUÇÃO

Projetos de sistemas digitais, chamados de esquemas, são compostos de diagramas interligados. Essa abordagem visual para descrever um circuito digital é intuitiva, mas torna-se impraticável à medida que a complexidade aumenta. Outra maneira de descrever circuitos digitais é usar uma linguagem textual que se destina especificamente a capturar de forma clara e concisa as características definidoras do projeto digital.

Neste contexto, projetos de sistemas digitais usando Linguagens de Descrição de Hardware (Hardware Description Language – HDL) é um campo com potencial grande de crescimento na atualidade. As aplicações dos projetos digitais estão presentes em nosso dia a dia, incluindo computadores, calculadoras e câmeras de vídeo etc.

As linguagens de descrição de hardware permitem que você descreva um circuito usando palavras e símbolos e, em seguida, o software de desenvolvimento pode converter essa descrição textual em dados de configuração que são carregados no FPGA (Field Programmable Gate Arrays) para implementar a funcionalidade desejada. As linguagens de descrição de hardware mais populares são Verilog e VHDL. Elas são amplamente utilizadas em conjunto com FPGAs, que são dispositivos digitais projetados especificamente para facilitar a criação de circuitos digitais customizados.

A modelagem de Unidade de Ponto Flutuante (UPF) eficiente pode executar as funções básicas e transcendentais com complexidade reduzida. As atividades envolvidas para implementação são: a manipulação de dados de ponto flutuante, a conversão de dados para o formato IEEE 754, a execução de qualquer uma das seguintes operações aritméticas como adição, subtração, multiplicação, divisão e operação de deslocamento e operações transcendentais como raiz quadrada, seno de um ângulo e cosseno de um ângulo.

Do ponto de vista da arquitetura, a UPF é um coprocessador que opera em paralelo com a unidade inteira do processador. A UPF obtém suas instruções da mesma instrução do decodificador e sequenciador e compartilha o barramento do sistema. Além disso, a Unidade Lógica e Aritmética (ULA) e a UPF operam independentemente e em paralelo. No caso da Intel, a microarquitetura de um processador Intel varia entre as várias famílias de processadores. Por exemplo, o processador Pentium Pro tem duas unidades inteiras e duas UPFs; enquanto, o processador Pentium tem duas unidades inteiras e uma UPF, e o processador Intel486 tem uma unidade inteira e uma UPF (Intel, 1999).

Cada geração de UPFs das arquiteturas de computadores atualmente são projetadas para fornecer estabilidade, resultados precisos quando programados usando algoritmos simples de “lápis e papel”, trazendo a funcionalidade e o poder da computação numérica precisa para o usuário final. O padrão IEEE 754 aborda especificamente essa questão, reconhecendo a importância fundamental de tornar os cálculos numéricos fáceis e seguros de usar.

Para executar qualquer operação aritmética, os usuários devem ter o conhecimento sobre a representação de ponto flutuante de acordo com o padrão IEEE 754 para fornecer entrada para o UPF, ou deve-se ter um conversor que pode converter o número decimal para o formato IEEE 754 e fornecer esses valores como entrada da UPF. Depois de executar a operação, o UPF fornece a saída em termos do formato IEEE 754. Assim, um conversor pode converter esse formato em representação decimal e fornecer a saída como um sistema numérico decimal. Desse modo, os usuários que não conhecem o formato IEEE 754 também podem usar esta unidade aritmética.

Este trabalho apresenta a implementação de uma UPF de 32 bits baseada no padrão IEEE 754, utilizando a linguagem Verilog com o objetivo de projetar e simular a unidade durante a implementação da operação aritmética de divisão.

ESTADO DA ARTE

Özkılbaç e Karacalı (2021) publicaram em seu artigo uma proposta de Unidade de Ponto Flutuante (UPF) de 32 bits, que implementa as operações de multiplicação, divisão, adição e subtração baseadas no padrão IEEE 754, usando FPGA parte do circuito integrado Xilinx Zynq-7000. A linguagem de programação utilizada é VHDL. A UPF foi projetada para o processador ARM que é parte do mesmo circuito. Um sistema que se comunica com o PC via UART foi projetado usando o Zedboard Development Kit. Importante notar que com relação à operação de divisão, o algoritmo básico da operação em ponto flutuante consiste em realizar a diferença dos valores dos expoentes e dividir os valores das frações. A divisão de dois números binários de mesmo comprimento é feita com algoritmo de comparação usando comparador de magnitude. Ao projetar a operação de divisão de ponto flutuante, a probabilidade dos operadores serem zero ou infinitos deve ser levada em consideração.

Nair et al. (2020) publicaram em seu trabalho do Usha Mittal Institute of Technology na Índia, a implementação de uma UPF de 32 bits, baseada no padrão IEEE 754 para as operações de adição, subtração, multiplicação e divisão. Os algoritmos são simulados usando o ModelSim em Verilog HDL. As diferentes operações realizadas mostraram uma precisão de 88% em comparação com os resultados calculados manualmente. O atraso para a unidade de adição foi de 5,591ns e o tempo de execução da CPU foi de 7,44 segundos. O atraso para o multiplicador é de 3,643 ns. Para a unidade divisora, a utilização do registrador de corte é de 1% e os pares LUT-FF de 3%. No caso de o processador completo funcionar, o tempo total da CPU para conclusão da execução é de 47,97 segundos, atraso de 10,004 ns. Os autores sugeriram como trabalho futuro a mesma modelagem para UPF de dupla precisão (64 bits).

Rudani e Saviya (2020) desenvolveram uma UPF, onde a entrada deve ser fornecida no formato IEEE 754, que representa valores de ponto flutuante de precisão simples de 32 bits. A principal aplicação desta unidade aritmética está no coprocessador matemático, geralmente conhecido como processador DSP (Digital Signal Processor). No DSP, para o processamento do sinal, é necessário um valor com alta precisão e por ser um processo iterativo, o cálculo deve ser o mais rápido possível. Todos os módulos, incluindo adição, subtração, multiplicação e divisão, foram escritos usando Verilog HDL e, em seguida, compilados e simulados no software de design Altera QuartusII.

Koteswara e Srinivasa (2018) implementaram uma aritmética inexata de ponto flutuante binário de 32 bits que inclui as operações de soma, subtração e multiplicação de ponto flutuante com desempenho melhorado em relação aos métodos convencionais. Neste trabalho, a arquitetura em pipeline é usada para aumentar o desempenho e aumentar a frequência de operação. Ao mesmo tempo, a lógica relacionada inclui o normalizador e o “arredondador” de acordo com as partes inexatas da mantissa e do expoente. As operações de ponto flutuante são manipuladas pelas unidades: FPadd, FPsub, FPmul. A unidade FPadd adiciona o valor no acumulador de ponto flutuante ao ponto flutuante acumulador. A unidade FPsub subtrai o valor no operando de ponto flutuante do acumulador de ponto flutuante. A unidade FPmul multiplica o valor no acumulador de ponto flutuante pelo operando de ponto flutuante. Neste projeto, a arquitetura proposta é simulada e sintetizado por Xilinx ISE 14.7.

Yadav e Chaudhary (2017) descrevem o processo detalhado para o cálculo das operações de adição, subtração e multiplicação em números de ponto flutuante, representados no formato IEEE 754 de 32 bits e projetado em linguagem VHDL. O projeto foi simulado e sintetizado num módulo FPGA Vitex 5, a fim de identificar a área ocupada e seu desempenho em termos de atraso. A simulação mostra que as unidades de pré-normalização e pós-normalização da UPF podem ser otimizadas para reduzir a necessidade de hardware, bem como o atraso. A unidade de ponto flutuante foi projetada, simulada e então sintetizada para obter seu desempenho em termos de área ocupada e atraso no Vitex 5 FPGA Module. No caso do caminho de dados opb_in_fpu até opb_in_sig_0, o atraso lógico combinacional total e o atraso de roteamento é de 1,154 ns e o atraso total de estouro a estouro é de 3,259 ns.

Antony e Joseph (2016) implementaram um comparador de números em ponto flutuante de dupla precisão, com a vantagem adicional de lidar com os casos inválidos. A representação de números de ponto flutuante é baseada no padrão IEEE 754. Aproveitando ao máximo a arquitetura de árvore de prefixo paralelo, o projeto deste comparador primeiro compara o bit mais significativo e prossegue em direção ao bit menos significativos apenas quando os bits comparados são iguais. O comparador foi projetado em Verilog HDL e sintetizado no Xilinx ISE 14.6 visando Virtex 5 e a ferramenta Cadence Encounter. Os resultados mostram que a nova arquitetura do comparador é eficiente no tratamento de todos os números de ponto flutuante inválidos.

FUNDAMENTAÇÃO TEÓRICA

Linguagem Verilog

A Verilog Hardware Description Language (Verilog HDL) é uma linguagem que descreve o comportamento de circuitos eletrônicos, mais comumente circuitos digitais. Verilog HDL é definida pelos padrões do IEEE. Existem três variantes comuns: Verilog 1995, Verilog 2001 e o recente SystemVerilog 2005. Verilog HDL pode ser utilizada para projetar hardware e criar entidades de teste para verificar o comportamento de uma peça de hardware. Verilog HDL é usada por uma variedade de ferramentas EDA (Electronic Design Automation), incluindo ferramentas de síntese como Quartus® Prime Integrated Synthesis, ferramentas de simulação e ferramentas de verificação formal.

A padronização atual da linguagem Verilog, definida em IEEE 1364-2005, provê uma clara relação entre a descrição por meio da sintaxe da linguagem de descrição de hardware e o diagrama esquemático do hardware físico, sendo que um módulo da linguagem é utilizado para propósitos de síntese e a linguagem completa pode ser utilizada para modelagem e simulação. Verilog suporta a projeção, verificação e implementação de projetos analógicos, digitais e híbridos em vários níveis de abstração. Uma das características principais da modelagem de circuitos digitais por meio de uma linguagem descritiva de hardware em relação à modelagem esquemática é a independência da plataforma de desenvolvimento no projeto de circuitos digitais (Cavanagh, 2010).

LaMeres (2019) publicou um livro que apresenta uma introdução à linguagem Verilog para modelar, simular e sintetizar a lógica combinacional. O livro cobre lógica sequencial e máquinas de estado finito no nível estrutural e sistemas síncronos sofisticados a serem modelados. Vários exemplos de modelagem de sistemas sequenciais e os detalhes de lógica programável, memória de semicondutor e circuitos aritméticos são apresentados. O livro culmina com uma discussão sobre design de sistema de computador. Cada componente de um sistema de computador é descrito com a implementação do Verilog, ao mesmo tempo em que reforça continuamente o hardware subjacente à abstração HDL.

Conforme descrito no manual de referência, tem-se duas descrições de circuitos que podem ser utilizadas na linguagem por Xilinx (1999):

Uma descrição de circuito Verilog pode ser de dois tipos; uma estrutural descrição ou descrição funcional, também chamada de Registro Descrição do nível de transferência (RTL). Uma descrição estrutural define a composição física exata do circuito, detalhando os componentes e o conexões entre eles. Uma descrição funcional ou RTL descreve um circuito em termos de seus registradores e a lógica combinatória entre os registradores.

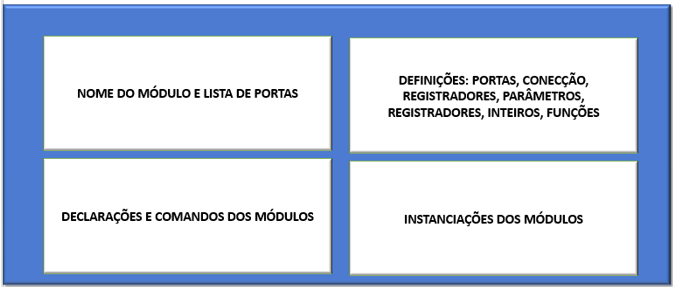

A principal entidade da linguagem Verilog é um módulo. Um módulo consiste basicamente no nome do módulo, sua descrição de entrada e saída (definição de porta), uma descrição da funcionalidade ou implementação do módulo (instruções e construções do módulo) e instanciações nomeadas. As partes estruturais básicas de um módulo são mostradas na figura 1.

Figura 1 – Estrutura dos módulos

Padrão IEEE 754

O padrão IEEE 754 é uma especificação amplamente adotada para representação e aritmética de números de ponto flutuante em sistemas de computador. Foi desenvolvido pelo Instituto de Engenheiros Eletricistas e Eletrônicos (IEEE, 1985) e publicado inicialmente em 1985, com revisões e atualizações ao longo dos anos.

O padrão IEEE 754 define formatos de representação para números de ponto flutuante, incluindo números reais e operações aritméticas sobre eles. Os números de ponto flutuante são representados usando uma combinação de sinal, expoente e mantissa. O formato mais comum é conhecido como binary32 ou single precision ou precisão simples que usa 32 bits para representar um número de ponto flutuante, enquanto o formato binary64 ou double precision ou precisão dupla faz o uso de 64 bits.

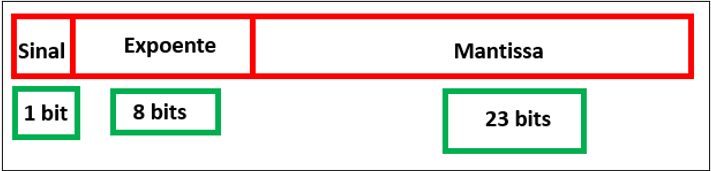

Os números reais em um formato binário de ponto flutuante são representados em três partes: um sinal, uma mantissa (também chamada de significando) e um expoente. A figura 2 ilustra o formato binário de ponto flutuante em precisão simples (32 bits). No caso da precisão simples: s = 1, e = 8 e f = 23 bits, totalizando N = 32 bits, ou seja, N = s + e + f, correspondendo ao tamanho da palavra em bits.

Figura 2 – Formato de ponto flutuante (base 2)

Um primeiro ponto importante no formato IEEE 754 diz respeito ao expoente. Para facilitar as implementações, o expoente é polarizado (bias em inglês), ou seja, trabalha-se sempre com expoente positivo. Deste modo, para o caso de 32 bits o padrão recomenda somar 127 ao expoente. (Viana, 2022).

O padrão IEEE 754 trabalha com o número em ponto flutuante normalizado, ou seja, o primeiro dígito (d1) deve ser diferente de zero para assegurar a unicidade de representação, e manter sempre a precisão máxima suportada pela mantissa (Vianna, 2022). A figura 3 mostra um exemplo de um número decimal em formato IEEE 754 na base 2:

Figura 3 – Número no formato IEEE 754 normalizado e polarizado

De forma geral pode-se resumir o formato como sendo:

Uma das características principais do padrão IEEE 754 é a capacidade de representar números em uma ampla faixa de magnitudes, desde valores muito pequenos até valores muito grandes. Além disso, ele fornece um mecanismo para representar números especiais, como o infinito positivo e negativo, e valores especiais como NaN (Not a Number) para indicar resultados inválidos ou indefinidos.

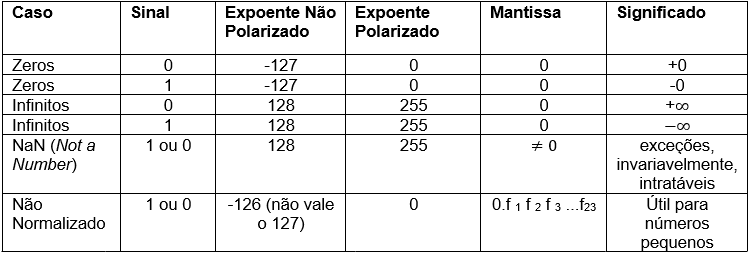

Deste modo, os formatos de ponto flutuante incluem alguns valores tratados de maneira especial, chamados de classes especiais, conforme mostrado no quadro 1.

O padrão IEEE 754 também define as regras para realizar operações aritméticas básicas, como adição, subtração, multiplicação e divisão, sobre números de ponto flutuante. Essas operações são projetadas para fornecer resultados com precisão e com o mínimo de erros de arredondamento possível.

Quadro 1 – Classes especiais de representação do Formato IEEE 754

No entanto, é importante destacar que o padrão IEEE 754 tem algumas limitações e que os erros de arredondamento ainda podem ocorrer em certas situações. Além disso, outros padrões e extensões foram propostos para melhorar as propriedades numéricas e a precisão dos cálculos de ponto flutuante, como o IEEE 754-2008 e o IEEE 754-2019.

Em resumo, o padrão IEEE 754 é uma especificação que define como os números de ponto flutuante são representados e como as operações aritméticas são realizadas em sistemas de computador. Ele fornece uma base sólida para o processamento de números de ponto flutuante, sendo amplamente adotado em diferentes plataformas e linguagens de programação.

Unidade de Ponto Flutuante (UPF)

Uma UPF é um componente essencial de um processador de computador responsável por realizar operações aritméticas em números de ponto flutuante, seguindo as especificações do padrão IEEE 754.

A UPF consiste em uma série de circuitos e lógica projetados para lidar com a representação, manipulação e cálculos de números de ponto flutuante. Ela é responsável por converter os números de ponto flutuante em representações internas adequadas, realizar as operações matemáticas necessárias e fornecer o resultado no formato correto.

Ao trabalhar com números de ponto flutuante, a unidade de ponto flutuante deve levar em consideração aspectos como a precisão dos números, os intervalos de valores representáveis e as regras de arredondamento definidas pelo padrão IEEE 754.

Geralmente, a UPF é projetada com diferentes componentes, incluindo registradores de dados para armazenar os operandos e resultados, circuitos para executar operações aritméticas (como adição, subtração, multiplicação e divisão) e lógica de controle para coordenar as operações.

A unidade de ponto flutuante também lida com situações especiais, como números infinitos, NaN (Not a Number) e operações com valores nulos, garantindo que os resultados sejam tratados corretamente conforme definido no padrão IEEE 754.

A eficiência e a precisão da unidade de ponto flutuante podem variar entre diferentes arquiteturas de processadores. Alguns processadores podem ter unidades de ponto flutuante dedicadas e altamente otimizadas, enquanto outros podem compartilhar recursos com a Unidade de Processamento Central (CPU Central Processing Unit), o que pode resultar em desempenho ligeiramente inferior.

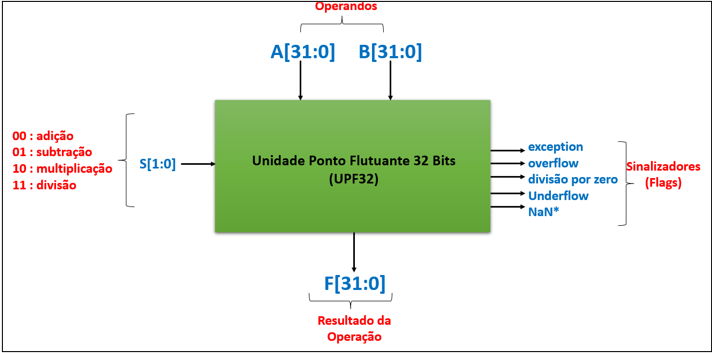

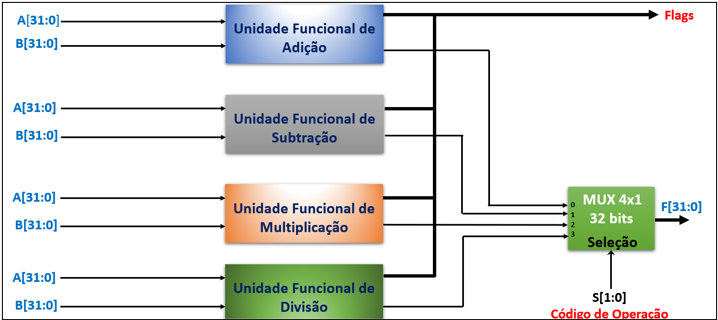

Figura 4 – Visão geral da UPF

As operações matemáticas tais como, como adição, subtração, multiplicação ou divisão, são realizadas pela ULA ou pela UPF. Quando uma CPU recebe uma instrução, ela a envia automaticamente para o processador correspondente. Por exemplo, 42 + 6 seria processado como um cálculo inteiro pela ULA, enquanto 42,5693245 + 5,458789 seria enviado para a UPF.

A Figura 4 ilustra a visão geral da UPF de 32 bits, onde as entradas A e B de 32 bits representam os operandos, e a entrada de 2 bits representa os códigos de operação (adição, subtração, multiplicação e divisão). Os dois bits combinados S1 e S0 (00: adição, 01: subtração, 10: multiplicação e 11: divisão) identificam a unidade funcional da UPF que realiza a operação correspondente. O sinal de saída F de 32 bits representa o resultado da última operação realizada pela UPF, e os outros 5 bits de saída sinalizam o estado do resultado da UPF.

Do modo geral, UPF pode realizar as seguintes operações:

Adição: A operação de adição em uma UPF envolve a soma de dois números de ponto flutuante. Os números são alinhados com base nos seus expoentes, e então as mantissas são somadas. O resultado é normalizado e arredondado, se necessário, de acordo com as regras do padrão IEEE 754.

Subtração: A subtração em uma UPF é semelhante à adição. Os números são alinhados e as mantissas são subtraídas. O resultado passa pelo processo de normalização e arredondamento, seguindo as regras do padrão IEEE 754.

Multiplicação: A multiplicação em uma UPF envolve a multiplicação das mantissas dos números de ponto flutuante e a soma dos expoentes. O resultado é normalizado e arredondado, se necessário, de acordo com as especificações do padrão IEEE 754.

Divisão: A divisão em uma UPF é realizada dividindo as mantissas dos números de ponto flutuante e subtraindo os expoentes. O resultado passa pelo processo de normalização e arredondamento de acordo com as regras definidas no padrão IEEE 754.

Além dessas operações básicas, as UPF também podem suportar operações mais avançadas, como raiz quadrada, exponenciação e logaritmo. Essas operações envolvem algoritmos mais complexos e podem exigir mais ciclos de clock para serem executadas.

PROJETO DA UPF DE 32 BITS

A modelagem proposta neste trabalho tem com base o trabalho de Özkılbaç e Karacalı (2021). A UPF de 32 bits é modularizada em unidades funcionais, como mostra a Figura 5. As quatro unidades funcionais são nomeadas da seguinte forma: Unidade Funcional de Adição (UFA) e Unidade Funcional de Subtração (UFS), Unidade Funcional de Multiplicação (UFM) e Unidade Funcional de Divisão (UFD). Duas entradas (A e B) de 32 bits representam os operandos das respectivas unidades funcionais. As quatro unidades funcionais possuem uma saída de 32 bits, que representa o resultado da operação realizada, e outra saída que representa os flags que indicam o estado do resultado das unidades. O MUX 4:1 usa os bits da saída: S [1:0], que geram quatro combinações (00:adição; 01:subtração; 10:multiplicação; 11:divisão) para selecionar qual saída da unidade será aquela selecionada pela UPF.

Figura 5 – Unidades Funcionais da UPF de 32 Bits

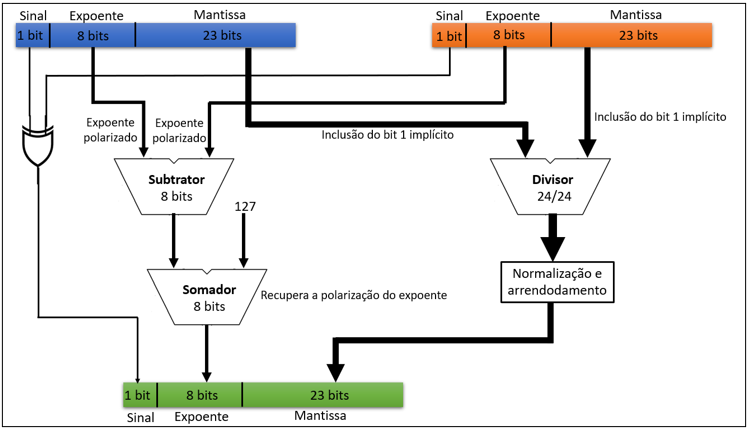

O principal foco deste trabalho é a análise, projeto e implementação da Unidade Funcional de Divisão (UFD). Para dividir dois números em ponto flutuante, 1.f1 x 2e1 ÷ 1.f2 x 2e2 (onde e1 e e2 são expoentes já polarizados), os seguintes passos devem ser executados, conforme mostrado na figura 6:

[1] Obter o sinal da divisão pela operação ou-exclusivo entre os bits de sinais dos operandos (dividendo e divisor): s1 xor s2 (sinais dos operandos);

[2] Subtrair os expoentes: subtrair e2 de e1 e somar 127 (011111112) para recuperar a polarização inicial dos operandos, e1-e2+011111112;

[3] Obter a divisão das mantissas: realizar a divisão das mantissas com o bit 1 implícito decorrente da normalização dos operandos;

[4] Normalizar o resultado, se necessário (como por exemplo o resultado da divisão seja igual a 0.1xxxx…x. Neste caso desloca-se o ponto decimal uma vez para a direita e subtrai-se 1 do expoente determinado no passo 2);

[5] Arredondar o resultado para caber nos bits disponíveis da mantissa, no caso 23 bits;

[6] Determinar os flags de ocorrência de divisão por zero, underflow, overflow, ou se a operação é inválida (NaN), observa-se que este passo não está mostrado na figura 6.

Figura 6 – Visão geral da Unidade Funcional de Divisão (UFD)

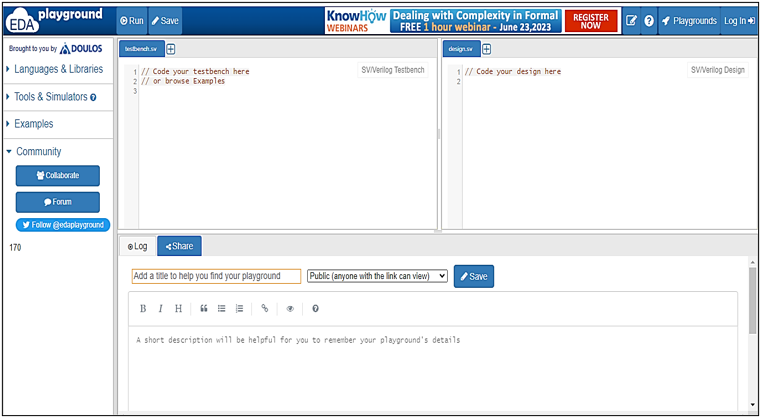

A implementação em linguagem Verilog pode ser realizada com várias IDEs baseados em Verilog com FPGAs Altera e Xilinx (1999) que são suportados pelo Altera Quartus II e Xilinx ISE IDEs disponíveis no mercado. Neste trabalho foi utilizado o EDA Playground (2023).

O EDA Playground (2023) mostrado na figura 7 é uma plataforma online que oferece um ambiente de desenvolvimento e simulação de projetos de eletrônica digital. Ele permite que engenheiros, estudantes e entusiastas da área projetem e testem circuitos digitais de maneira conveniente e interativa. Através do EDA Playground, os usuários podem escrever e testar códigos em diversas linguagens de descrição de hardware, como Verilog, VHDL e SystemVerilog. Eles também podem criar e simular circuitos digitais utilizando uma ampla variedade de componentes lógicos, como portas lógicas, registradores, flip-flops etc.

Uma das vantagens do EDA Playground é a sua simplicidade e facilidade de uso. Não é necessário instalar nenhum software ou configurar ambientes de desenvolvimento complexos. Os usuários podem começar a projetar e simular seus circuitos imediatamente, economizando tempo e recursos.

Figura 7 – EDA Playground

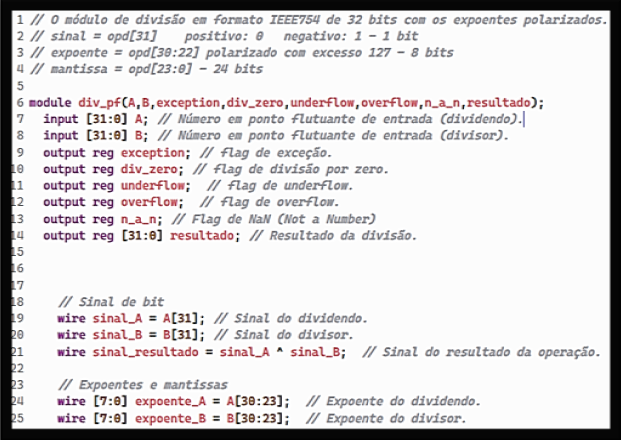

A implementação em Verilog do algoritmo da divisão é mostrada nas figuras 8, 9, 10 e 11.

A figura 8 mostra a parte do código relativa definição dos tipos de dados.

Figura 8 – Código Verilog da UFD – Parte 1

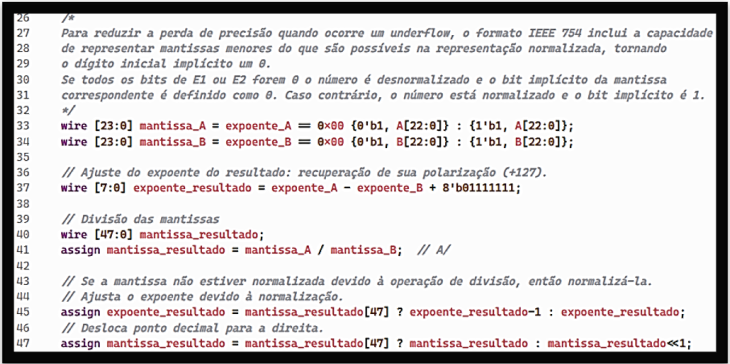

A figura 9 mostra a parte do código referente ao ajuste de expoentes e a divisão propriamente dita.

Figura 9 – Código Verilog da UFD – Parte 2

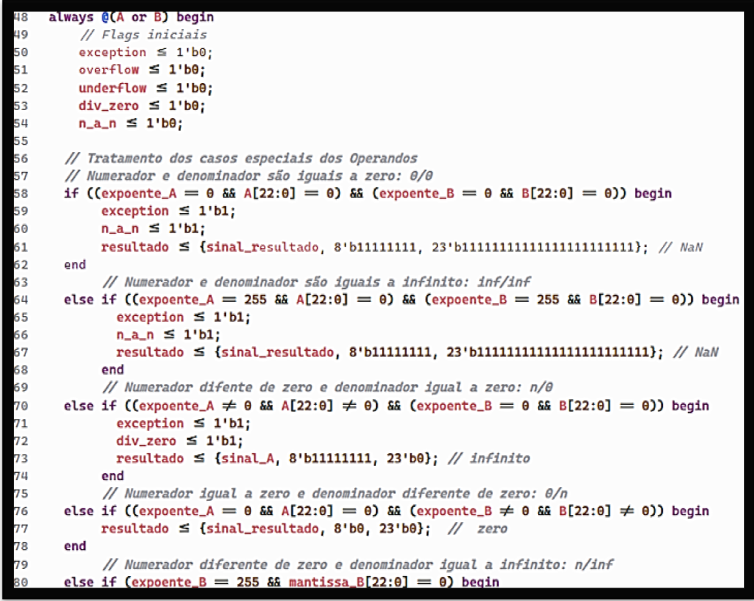

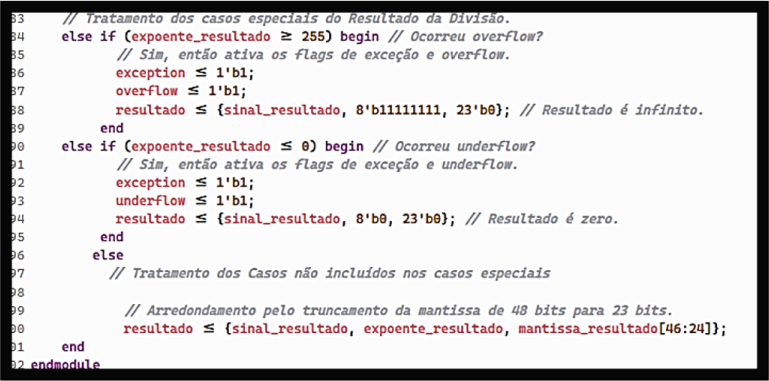

A figura 10 ilustra a parte do código referente ao tratamento dos casos ou classes especiais.

Figura 10 – Código Verilog da UFD – Parte 3

A figura 11 mostra a continuação do código de tratamento e a inclusão do arredondamento pelo truncamento da mantissa de 48 bits para 23 bits.

Figura 11 – Código Verilog da UFD – Parte 4

RESULTADOS E DISCUSSÃO

O TestBench é uma parte importante da linguagem de descrição de hardware Verilog utilizada para a simulação e verificação de circuitos digitais. Ele descreve um ambiente de teste para o circuito a ser projetado, permitindo a aplicação de estímulos e a observação dos resultados. O TestBench é um módulo Verilog especializado que não faz parte do circuito principal, mas é criado para testar e validar o comportamento do design. Ele consiste em uma série de estímulos e verificações que são aplicados ao circuito, permitindo a simulação de diversos cenários e situações de teste.

Ao escrever um TestBench em Verilog, é comum utilizar registradores ou sinais para fornecer os estímulos de entrada para o circuito. Esses estímulos podem ser sequências de bits ou sinais de clock que simulam o comportamento do sistema real. O TestBench também pode incluir a inicialização de sinais de entrada, a criação de formas de onda complexas ou até mesmo a geração de estímulos aleatórios para fins de teste.

Além disso, o TestBench também inclui verificações para garantir que o circuito esteja operando corretamente. Isso pode envolver a comparação dos resultados esperados com os resultados simulados ou a verificação de sinais de saída em relação a critérios de aceitação definidos. Essas verificações são importantes para garantir que o circuito esteja funcionando de acordo com as especificações e atenda aos requisitos de projeto.

A simulação do TestBench é realizada por meio de ferramentas de simulação Verilog, que permitem a execução de testes e a observação dos resultados. Durante a simulação, o TestBench pode registrar informações sobre o comportamento do circuito, como atrasos de propagação, tempos de resposta e valores dos sinais em diferentes momentos.

O TestBench é uma ferramenta essencial para a verificação e validação de circuitos digitais em Verilog. Ele permite aos projetistas testar o comportamento do circuito em diferentes cenários e garantir que ele atenda às especificações. Ao desenvolver um TestBench bem projetado, é possível obter uma visão abrangente e precisa do desempenho e do funcionamento do circuito digital, ajudando a identificar possíveis problemas e aprimorar o design.

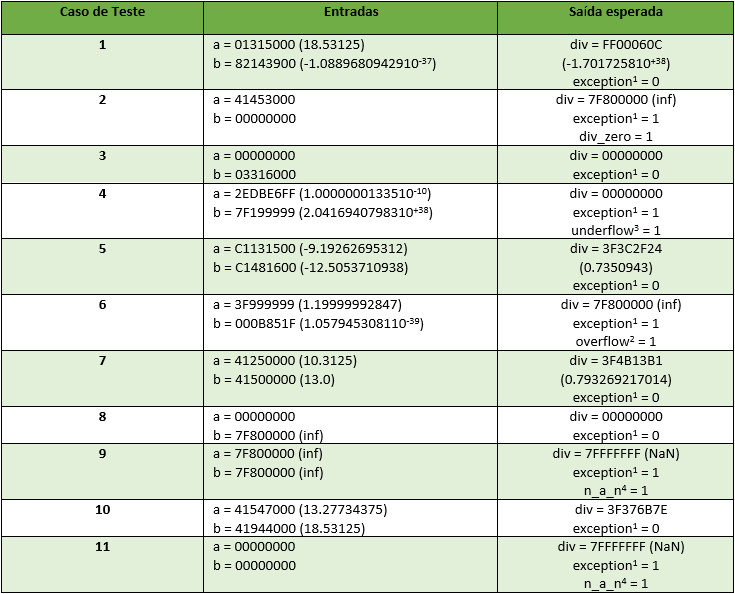

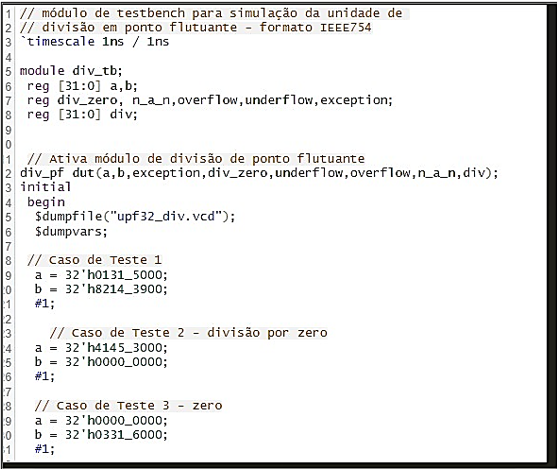

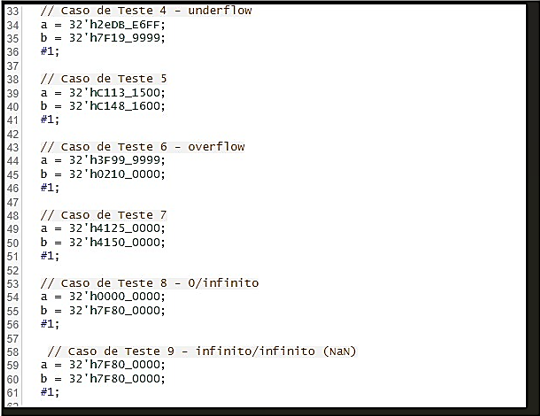

O quadro 2 mostra 11 casos de teste que serão simulados para a UFD. Deve-se observar que todos os números hexadecimais estão em formato IEEE 754 de 32 bits com expoentes polarizados. Eles são empregados na bancada de testes para a simulação dos resultados para casos típicos de decisão, casos que resultam em operações inválidas, e os casos para simular overflow e underflow.

É importante ressaltar que a bancada de teste é um arquivo em Verilog que não possui entradas ou saídas. Na verdade, ocorre um “instanciamento“ do sistema a ser testado como um módulo de nível inferior. O sistema que está sendo testado é frequentemente chamado de dispositivo em teste (DUT) ou unidade em teste (UUT).

Quadro 2 – Casos de Teste da UFD de 32 Bits

1exception: sinal de saída da UPF32 que sinaliza a ocorrência de uma exceção, seja devido a um dos operandos que resulta em uma operação inválida, ou devido ao resultado da operação que seria inválido.

2overflow: ocorre quando uma operação aritmética resulta em uma magnitude maior do que pode ser expressa com um expoente de 128: Exemplo: 2^120 / 2^-100 = 2^220.

3underflow: ocorre quando a magnitude fracionária é muito pequena com um expoente abaixo de -127: Exemplo: 2^-120 * 2^100 = 2^-220.

4n_a_n (NaN – Not a Number): ocorre quando de uma tentativa de operação de divisão inválida: 0/0, inf/inf, etc.

Obs:

(1) todos os números hexadecimais em formato IEEE 754 32 bits com expoentes polarizados.

(2) Números decimais entre parênteses.

(3) inf: infinito

Fonte: Autores

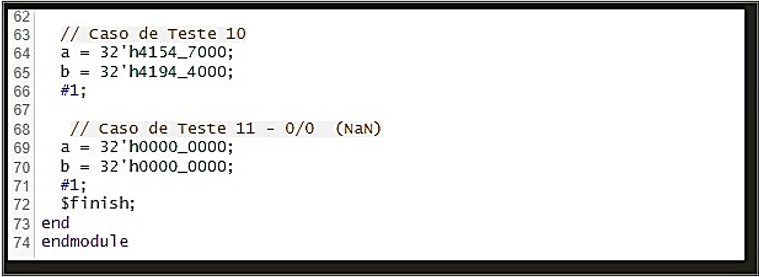

O código Verilog da bancada de teste para a simulação para a unidade funcional de multiplicação é mostrado nas figuras 12 a 14.

Figura 12 – Código da Bancada de Teste – UFD – Parte 1

Figura 13 – Código da Bancada de Teste – UFD – Parte 2

Figura 14 – Código da Bancada de Teste – UFD – Parte 3

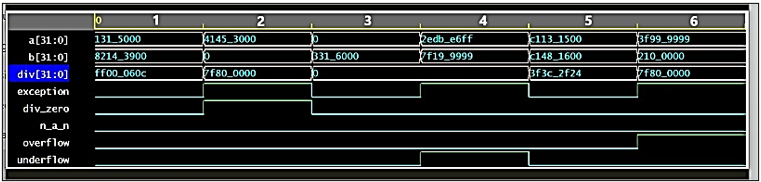

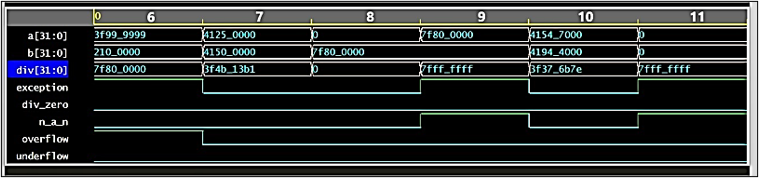

As figuras 15 e 16 mostram os resultados da simulação, no formato de formas de onda quadradas para os onze testes descritos no quadro 2 para a UFD.

Figura 15 – Resultados da Simulação dos casos de teste (1 a 6) – Parte 1

Figura 16 – Resultados da Simulação dos casos de teste (6 a 11) – Parte 2

CONSIDERAÇÕES FINAIS

O formato de número de ponto flutuante IEEE 754 é usado hoje em sistemas de computador, uma vez que as operações em ponto flutuante neste formato tornam-se mais fáceis de serem processadas. Porém, com relação às operações básicas de adição, subtração, multiplicação e adição têm ainda um campo enorme de pesquisa para propor algoritmos mais eficientes que consigam implementar estas operações no menor tempo possível e com o menor gasto de energia em circuitos lógicos.

Neste estudo, uma UPF com foco na operação de divisão no formato de número de ponto flutuante IEEE 754 de 32 bits foi projetada usando a linguagem de programação Verilog.

A unidade funcional de divisão foi implementada em linguagem Verilog utilizando a plataforma EDA Playground. Onze casos de testes foram simulados, envolvendo situações que podem acontecer no resultado da operação tais como: overflow, underflow e exceções (NaN, infinito). Os resultados apresentados pela simulação nos onze casos de teste foram àqueles esperados para este tipo de operação com ponto flutuante.

As aproximações ocorrem devido ao arredondamento da divisão das mantissas, pois o resultado desta operação deve ser representado em 23 bits. Outra aproximação deve-se ao fato que os operandos chegam à unidade de divisão convertidos em binários, no padrão IEEE 754, independentemente do formato trabalhado, esta aproximação é inevitável pois a maioria dos valores em ponto flutuante necessitam de uma quantidade infinita de bits.

Assim, para trabalhos futuros, pode-se implementar um conversor para converter o número decimal para o formato IEEE 754 e fornecer esses valores como entrada da UPF. Depois de executar a operação, a UPF fornece a saída em termos do formato IEEE 754. Um conversor pode converter esse formato em representação decimal e fornecer a saída como um sistema numérico decimal. Dessa forma, os usuários que não conhecem o formato IEEE 754 também podem usar esta unidade aritmética.

REFERÊNCIAS

ANTONY, P.; JOSEPH, A. Design and Implementation of Double Precision Floating Point Comparator. Procedia Technology, 2016, Vol. 25. https://doi.org/10.1016/j.protcy.2016.08.141, pages 528-535. Available online at ScienceDirect. Disponível em: <https://www.sciencedirect.com/science/article/pii/S2212017316304881>. Acesso em: 08 de mar. 2023.

CAVANAGH, Joseph. Computer Arithmetic and Verilog HDL Fundamentals. Boca Raton: CRC Press Taylor & Francis Group, 2010.

EDA Playground. Disponível em: https://edaplayground.com. Acesso em: 28 de mar. de 2023.

IEEE. American National Standards Institute / Institute of Electrical and Electronics Engineers: IEEE Standard for Binary Floating-Point Arithmetic, ANSI/IEEE Std 754-1985, New York, 1985.

INTEL. Intel Architecture Software Developer’s Manual. 1999. Volume 1: Basic Architecture. Disponível em < https://www.cs.cmu.edu/~410/doc/Intel-arch.pdf >. Acesso em: 24 de mai. 2022.

KOTESWARA, R.; SRINIVASA, R. Design and implementation of 32-bit inexact floating point arithmetic unit. International Journal of Advances in Electronics and Computer Science, 2018, Vol. 5, Issue 2. ISSN: 2393-2835. Disponível em < https://www.iraj.in/journal/journal_file/journal_pdf/12-446-15234290626-12.pdf >. Acesso em: 10 de mar. 2023.

LAMERES, Brock J. Quick Start Guide to Verilog. Cham, Switzerland: Springer.

NAIR, H. et al.. Design and implementation of floating point processor. International Journal of Advance Research, Ideas and Innovations in Technology (IJARIIT), 2020, Vol. 6, Issue 3. ISSN: 2454-132X. e Published Online Jun. 2020 in IJARIIT Journal. Disponível em <https://www.ijariit.com/manuscripts/v6i3/V6I3-1456.pdf>. Acesso em: 06 de abr. 2023.

ÖZKILBAÇ, B.; SAVIYA, T. Implementation and design of 32 bit floating-point ALU on a Hybrid FPGA-ARM Platform. Journal of Brilliant Engineering 2, 2021, https://doi.org/10.36937/ben.2020.001.005, pages 25-61. Disponível em <https://www.acapublishing.com/dosyalar/baski/BEN_2019_16.pdf>. Acesso em: 17 de mar. 2023.

SANTOS, E. J. F. da. Implementação das operações de uma unidade de ponto flutuante de 32 bits baseada no padrão IEEE 754 em Verilog. 2022. Trabalho de Conclusão de Curso (Bacharelado em Engenharia Elétrica) – Universidade do Estado de Minas Gerais, Ituiutaba, 2022.

SAVIYA, Y.; RUDANI, J. Design and Simulation of 32-Bit Floating Point Arithmetic Logic Unit using Verilog HDL. International Research Journal of Engineering and Technology (IRJET), 2020, Vol. 7, Issue 12. e-ISSN: 2395-0056, p-ISSN: 2395-0072. E-Published Online Dec. 2020 in IRJET Journals. Disponível em <https://www.irjet.net/archives/V7/i12/IRJET-V7I12262.pdf>. Acesso em: 14 de abr. 2023.

VIANA, G. V. R. Padrão IEEE 754 para aritmética binária de ponto flutuante. Universidade Estadual do Ceará-Departamento de Estatística e Computação. 2022.UFCE. (Apostila). Disponível em < https://www.lia.ufc.br/~valdisio/download/ieee.pdf >. Acesso em: 24 de mar. 2023.

XILINX. Verilog Reference Guide. 1999. Disponível em < https://in.ncu.edu.tw/ncume_ee/digilogi/vhdl/Verilog_Reference_Guide.pdf#page=22&zoom=100,70,94> . Acesso em : 01 mai. 2023.

YADAV, A.; CHAUDHARY, I. DESIGN of 32-bit Floating Point Unit for Advanced Processors. Int. Journal of Engineering Research and Application, 2017, Vol. 7, Issue 6 (Part -5). e-ISSN: 2248-9622. DOI: 10.9790/9622-0706053946, pp.39-46. Disponível em <https://issuu.com/www.ijera.com/docs/g0706053946>. Acesso em: 28 de mar. 2023.

1 Discente do Curso de Engenharia Elétrica, Universidade do Estado de Minas Gerais|(UEMG)|, Unidade Ituiutaba. jordana.1592901@discente.uemg.br

2 Docente no Departamento de Engenharias e Sistemas de Informação, Universidade do Estado de Minas Gerais (UEMG), Unidade Ituiutaba. Katia.lopes@uemg.br.

3 Docente no Departamento de Engenharias e Sistemas de Informação, Universidade do Estado de Minas Gerais (UEMG), Unidade Ituiutaba. mauro.gazzani@uemg.br.