REGISTRO DOI: 10.5281/zenodo.10247203

Joao Alexandre de Carvalho Santana1

Resumo

Este documento busca aplicar conhecimentos de Eletrônica e outras disciplinas, a fim de exemplificar a interdisciplinaridade presente na Engenharia elétrica. Nesta ́atividade foram desenvolvidos circuitos sequenciais e máquina de estados finitas e utilizou-se de elementos de conversão analógico digital, conversão digital-analógica e memórias . A idéia do ́projeto era utilizar esses conceitos e realizar o controle de um motor de corrente contínua. Admitindo 4 estados de operação e 4 bits de entrada.

Index Terms—Máquina de Estados Finitas, Memoria EPROM, Conversor AD, Conversor DA

I. INTRODUÇÃO

O intuito do projeto foi controlar através da máquina de estados, sendo esse procedimento realizado através das seguintes convenções:

- Estado ++ sendo necessário elevar bruscamente a tensão em cima do motor;

- Estado + sendo necessário elevar a tensão em cima do motor;

- Estado ”ref”sendo necessário manter a tensão em cima do motor;

- Estado – sendo necessário diminuir a tensão em cima do motor.

Ao longo do projeto foi necessário adicionar alguns circuitos afim de viabilizar a integração das diferentes partes dessa aplicação.

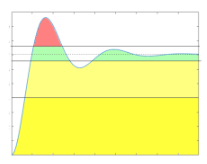

Figura 1. Exemplo com uma resposta genérica de um sistema ao degrau

Nessa resposta ao degrau fica mais visível o que cada estado irá representar no projeto proposto. O amarelo de maior brilho será o estado ”++”, o de amarelo de menor brilho o estado ”+”, verde estado de referência e a cor vermelha o estado -”

II. MATERIAIS E MÉTODOS

A. Conversor Analógico Digital

Para esse projeto foi utilizado um conversor analógico digital por aproximações sucessivas. Esse tipo de conversação é semelhante ao método numérico da bissecção ou ao algoritmo

computacional de busca binária em estrutura de dados como as árvores.

A tensão a ser convertida seria proveniente de um sinal vindo de um sensor, que poderia ser um tacógrafo, um sensor de efeito Hall mas para efeitos de simulação decidiu-se utilizar

de um potenciomêtro. A resolução desse conversor pode ser calculada da seguinte forma:

No caso como Vin foi 5 volts, a resolução do conversor foi 0.019V. Em relação ao tempo de conversão, essa grandeza estará condicionada ao clock ligado ao CI ADC0808. Durante as

simulações, utilizou-se um clock de 1kHz. O potenciomêtro nessa configuração permitirá uma tensão que irá de 0 a 5V, como esse também é o valor de referência configurado no CI. Pode-se afirmar que o valor mínimo e máximo respectivamente serão :0= (00000000)2 , 5

= (11111111)2.

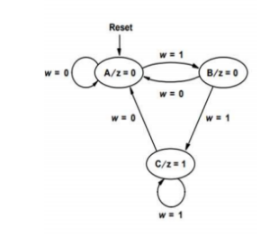

B. Máquina de Estados Finitos

A máquina de estados finitos (FSM) projetada foi do tipo MOORE, ou seja, a saída dela é condicionada pelo estado atual. Diferente da máquina MEALY onde a entrada tem

influência na saída.

Figura 2. Exemplo Máquina MOORE.

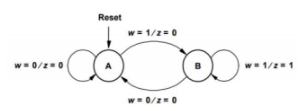

Figura 3. Exemplo Máquina MEALY.

A FSM executada no projeto foram admitido 4 bits de entrada vindos do conversor ADC. A respeito das entradas, cada informação foi associada um estado a ser forçando, assim

viabilizando a montagem da tabela verdade que gerou o circuito da FSM:

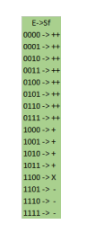

Figura 4. Ilustração dos estados futuros que são determinados pelo dado originado do ADC.

É importante pontuar que ao só analisar 4 bits do ADC ao ́invés de contemplar os 8 bits, foram perdidos aproximadamente 0,3V de informacão que são 16 vezes a resolução do

conversor analógico digital. Sobre a construção da máquina foram 4 bits de entrada mais 2 bits que representaram os estados.

Esses bits de estados foram convencionados da seguinte forma:

- Estado ++ como 00;

- Estado + como 01;

- Estado ”ref”como 10;

- Estado – como 11.

As saídas foram impostas da seguinte forma:

- Estado ++ teve sua saida como 11;

- Estado + teve sua saida como 10;

- Estado ”ref”teve sua saida como 01;

- Estado – teve sua saida como 00.

Uma outra característica desse projeto é que a entrada irá determinar o estado futuro da máquina de estados.

As saídas da máquina apresentam um significado físico pois implicam em uma informação de redução de tensão no caso do estado da cor vermelha conforme a Figura 1, também em uma ́informação de elevação do sinal como os estados em amarelo ou até de manutenção do sinal conforme o estado na cor verde são dados que serão convertidos posteriormente pelo conversor Digital Analógico, por serem 4 possíveis saídas, as mesmas podem ser representadas por 2 bits, sendo o MSB (SX) e o LSB (SY) para saída.

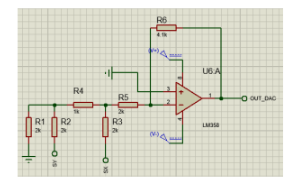

C. Conversor Digital Analogico

O conversor digital analógico (DAC) empregado, foi o de ́R-2R. Utilizando de um LM378, alimentado com tensões CC de -15 e 15V, R como 1K ohm e 2R sendo 2k ohm. O Ref a ser colocado na realimentação do amplificador operacional tinha o valor de 4.1k ohm(sendo esse valor obtido através dos resistores comerciais de 3.9K ohm em serie com o resistor de 200 ohm), dessa forma assegurando uma saída próxima de -5V.

Figura 5. Circuito do DAC R-2R.

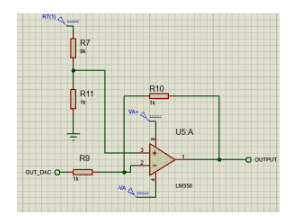

Afim de ter um valor positivo, foi adicionado um circuito analógico inversor, juntamente a ele foi realizado um Offset de 0.5V

Figura 6. Circuito inversor para utilização do sinal.

O sinal output será para colocar um transistor de junção bipolar (TBJ) em sua região ativa de operação, pois dessa forma será possível variar a corrente no coletor desse componente e assim controlar a queda de tensão em cima do motor.

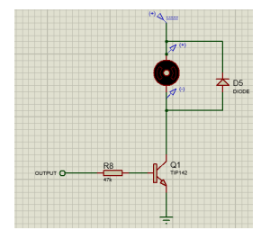

Figura 7. TBJ fazendo o driver para motor.

O motor foi colocado no coletor, sendo este alimentado com 10V contínuo e apesentando uma tensão nominal de 12V,em caso de precisar desligar o mesmo o diodo de roda livre

se mostra como um caminho alternativo para passagem de corrente. Neste circuito a resistência de base foi de 4.7k ohms(pois este é um valor comercial), de maneira que no caso no qual foi imposta a menor tensão possível entrando no ADC, houvesse uma tensão de 9,4V, diminuindo a queda de tensão no motor, com intuito de aumentar sua rotação, para o caso de maior tensão no ADC a tensão no motor será de 2,27V.

D. Memória

No projeto foi utilizado uma memória EPROM, que consiste em uma eletrônica programável dedicada somente para leitura, logo só permitiria gravar dados uma vez, a mesma se caracteriza como uma memória não volátil. Nesta aplicação, sua função foi guardar os dados que serão provenientes do ADC a cada ”X” segundos, sendo esta quantia estabelecida pelo clock. Em casos de um novo armazenamento será necessário reescrever a memória fazendo com que a informação previamente existente seja perdida.

Para fins de simulação usou-se o clock de 1Hz para melhor visualização durante a apresentação. O mapeamento foi realizado em instantes definidos pois possibilita conhecer

melhor o comportamento do motor durante a simulação. Uma vez que esses dados fossem apropriadamente armazenados na memória, o usuário poderá verificar se o motor foi devidamente controlado.

Figura 8. Circuito da memória.

Para que o endereço fosse incrementando a cada ”X” segundos, utilizou-se de um contador assíncrono de mod4096,com auxílio do 74LS93. O contador irá a cada pulso de clock alterar o endereço no qual a informação será registrada.

O contador foi de tal amplitude pois o motor tem um tempo de estabilização na ordem de milissegundos. Como a idéia é realizar o devido mapeamento do transiente e de instantes o

mesmo, a magnitude de 4096 endereços será uma abordagem satisfatória.

Figura 9. Contador que faz o acionamento da memória.

III. RESULTADOS

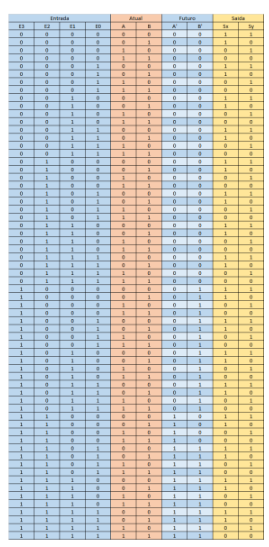

A tabela verdade realizada para encontrar o circuito da FSM foi:

Figura 10. Tabela Verdade para desenvolver a maquina de estados finito.

Sendo o principal elemento do projeto a FSM que se comporta como o componente a realizar à ação de controle.

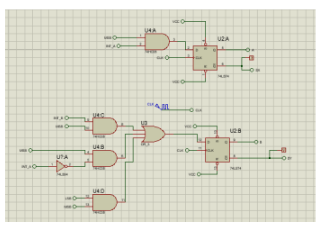

O circuito obtido para a mesma após a simplificação do mapa de Karnaugh.

Figura 11. Circuito da máquina de estados.

As equações obtidas através do mapa para definir a entrada dos Flip Flop tipo D foram as seguintes:

É importante pontuar que foi imposta a seguinte convenção de sinais:

- E3 como sinal MSB;

- E2 como sinal INT A;

- E1 como sinal INT B;

- E0 como sinal LSB.

O DAC irá realizar essa conversão para transformar o sinal digital em um sinal o qual iria entrar na base do TBJ assim acionando o motor. Como apontado na parte de Materiais e

Métodos para tornar essa aplicação mais interessante poderia ser utilizado de um sensor de Efeito Hall assim fechando a malha, tornando o sistema automatizado.

IV. CONCLUSÃO

Este trabalho teve como intuito mostrar conceitos que abrangem inúmeras disciplinas de engenharia desde eletrônica à teoria do controle. O sistema desempenhou conforme esperado, a lógica empregada pode ser devidamente ajustada para motores que solicitam maiores tensões uma vez que seja adicionado os devidos circuitos de tratamento de sinal.

REFERÊNCIAS

Erica, 1984. ́

[2] RONALD J. TOCCI; NEAL S. WIDMER; GREGORY L. MOSS.

SISTEMAS DIGITAIS – Princ ́ıpios e aplicac ̧oes. 11o Ed, 2014. 842p ̃

[3] JUNIOR, SERGIO L. Stevan. NOTAS DE AULA DISCIPLINA ELE-

TRONICA DIGITAL 2, 2020.

V. FOLHA DE SIMULAÇÃO

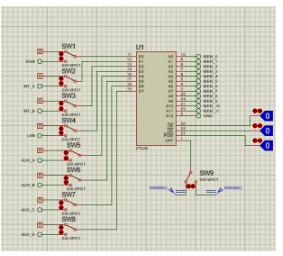

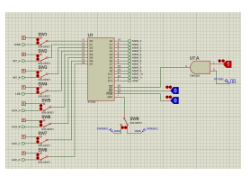

Esse anexo visa elucidar o usuário a respeito de usar o potenciometro para realizar a entrada no ADC. Uma vez vindo a informação do ADC, a máquina de estados irá receber

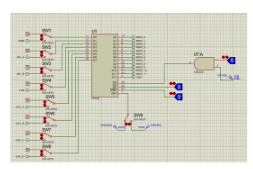

essa informação fazer o devido processamento do dado e assim transmiti-lo para o DAC. A informacão que está no DAC, será invertido e adequado com o amplificador inversor que tem o offset. No intuito de polarizar o TBJ na região ativa e, assim, variar a corrente no motor. A etapa que irá solicitar uma maior atenção do usuário será a gravação da memória. Pois VPP deverá estar na tensão em SW9(NC), o logic state em CE deverá estar em um e o clock, nele incluso, deverá estar em fase com o clock do contador que promove a alteração dos endereços. Na parte de recepção dos dados haverá chaves logo, é fundamental para a gravação, assegurar que os dados do ADC estejam devidamente ligados à memória. Conforme Figura 12 a estrutura para realizar a leitura dos dados da EPROM apresentaram mudanças especificamente em CE, nas chaves que estavam recebendo os dados e por fim na chave de VPP deverá estar na tensão em SW9(NO).

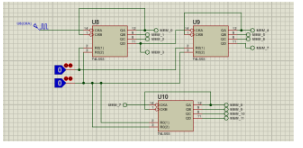

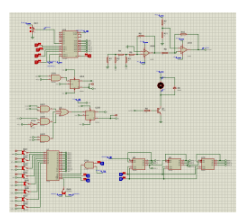

Conforme Figura 13 O circuito completo tera o seguinte esquemático Figura 14.

Figura 12. Ligações necessárias para gravar dados na memória.

Figura 13. Ligações necessárias para ler as informações contidas memória.

Figura 14. Circuito completo.

1Departamento Acadêmico de Eletrônica(DAELE) Universidade Tecnologica Federal do Paraná Ponta Grossa, Brasil jsantana@alunos.utfpr.edu.br